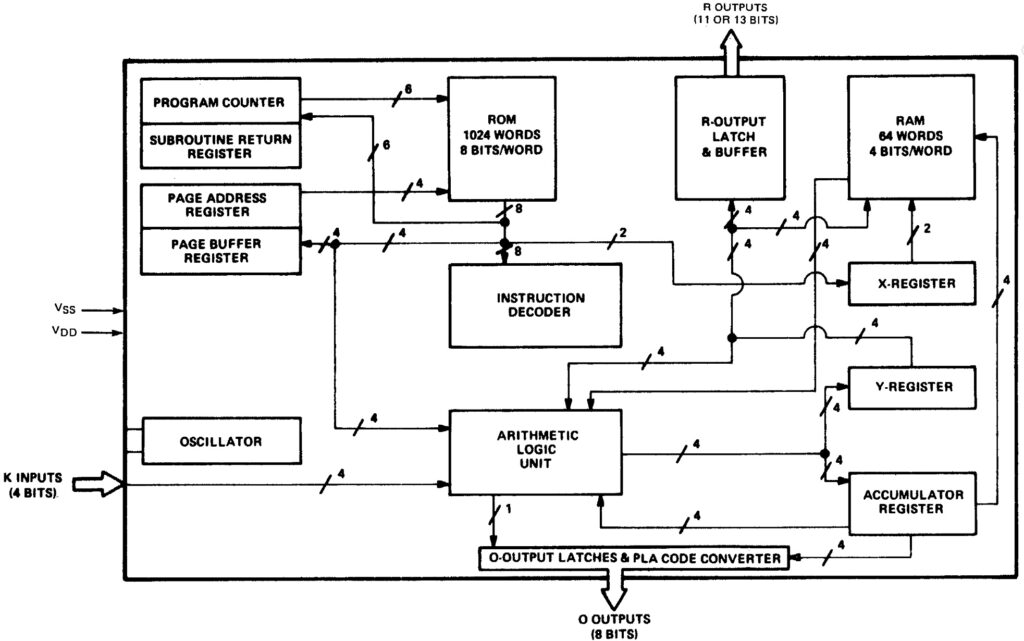

引き続きTMS-1000を題材にCPUを学習していきます。TMS-1000を構成するブロック毎の動作を仮説を立てて追ってみます。実物がないので実験できませんが後でマニュアルで確認します。

まずはOSCILLATORでクロック信号を発振します。内蔵しているOSCILLATORはRCなのかセラミックなのかクリスタルを使用しているのかわかりませんが矩形波を一定周期で出力しています。この信号が全てのブロックに伝わりますので各ブロックはその信号の都度に逐次状態を進めていきます。

電源投入後、各FFでできたレジスタの状態は不安定なのでリセットが必要です。リセットを行い全体を初期状態にします。

初期状態は命令の実行を待っている状態ですので次にプログラムカウンタが指す番地の命令を実行せよと何かしらの信号を与えます。

最初はプログラムカウンタが0なのでROMの0番地のビット列が命令デコーダに入ります。命令デコーダはその最初の命令(ビット列)に基づきFFでできているレジスタやバッファと論理回路の塊であるALUにビット列を送り命令を実行します。

次のクロック信号が来た時はプログラムカウンタ繰り上がります。前の命令を実行したので各レジスタの値が設定されている状態から最初と同じようにROMの次の番地のビット列を命令デコーダに送ります。

以下次々とクロック信号が変化する度にROMの命令が命令デコーダに送られます。例えばSUBROUTINE RETURNレジスタに次に実行する値を設定してからプログラムカウンタに飛んだ番地を書き込み、そこから新しい命令を実行し、SUBROUTINE RETURNの番地に戻すようなことでサブルーチンが実行できるように思えます。

こうしてみると命令デコーダが他のブロックに比べてだいぶ複雑な機構を持っているように見えます。

1 ROMからレジスタにビット列を複製する、RAMであればレジスタからRAMへ逆にRAMからレジスタへビット列の複製ができる。

2 使うレジスタを選択できる。

3 出力するバッファを選択できる。

4 ALUの演算を選択できる。

5 PROGRAM COUNTERやPAGE ADDRESS、SUBROUTINE RETURNを書き換え命令の実行順を変えることができる。

このようなことを実行するために命令のビット列ごとにどこをどうするか決定する回路になっていると思われます。

命令ごとに回路を作っていくとすると個人の手作りではTTLを使ったとしても4bitで十数個位が限度だと思います。ましてディスクリートトランジスタやリレーで作るとなったら数個の命令で根を上げそうです。

やはり1個数十円から買えるCPUは偉大な存在です。